Hello guys,

I'm studying the schematics trying to understand what different IC chips are doing. I have found one chip particulary interesting and I must admit I cannot understand what it is doing based on the data sheet.

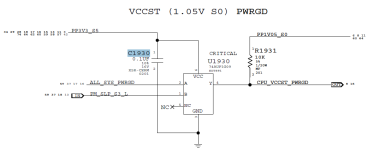

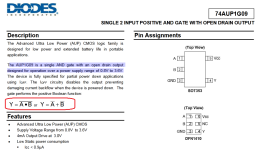

The schematics is shown in the attached picture. The output is used to produce 1.05V (PP1V05_S0). My first impression was that this is an logical AND gate. According to the datasheet: The AUP1G09 is a single AND gate with an open drain output designed for operation over a power supply range of 0.8V to 3.6V. But the actual Bollean formula is for NAND gate.

The complete datasheet is here: https://pdf1.alldatasheet.com/datasheet-pdf/view/473494/DIODES/74AUP1G09.html

Can you please clarify this?

This circuit is supplied by 3.3V. So, if both inputs (A and B) are high (3.3V), what is the output of this IC chip? From schematics it is supposed to be 1.05V after resistor 10 kOhm.

Thank you.

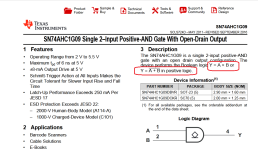

EDIT: This must be error in the data sheet because I found teh similar circuit produced by IT and there is different Boolean formula.

I'm studying the schematics trying to understand what different IC chips are doing. I have found one chip particulary interesting and I must admit I cannot understand what it is doing based on the data sheet.

The schematics is shown in the attached picture. The output is used to produce 1.05V (PP1V05_S0). My first impression was that this is an logical AND gate. According to the datasheet: The AUP1G09 is a single AND gate with an open drain output designed for operation over a power supply range of 0.8V to 3.6V. But the actual Bollean formula is for NAND gate.

The complete datasheet is here: https://pdf1.alldatasheet.com/datasheet-pdf/view/473494/DIODES/74AUP1G09.html

Can you please clarify this?

This circuit is supplied by 3.3V. So, if both inputs (A and B) are high (3.3V), what is the output of this IC chip? From schematics it is supposed to be 1.05V after resistor 10 kOhm.

Thank you.

EDIT: This must be error in the data sheet because I found teh similar circuit produced by IT and there is different Boolean formula.

Attachments

Last edited: